#

# Cascading Wafer-Scale Integrated Graphene Complementary Inverters under Ambient Conditions

Laura Giorgia Rizzi,<sup>†</sup> Massimiliano Bianchi,<sup>†</sup> Ashkan Behnam,<sup>‡,||</sup> Enrique Carrion,<sup>‡,||</sup> Erica Guerriero,<sup>†</sup> Laura Polloni,<sup>†,§</sup> Eric Pop,<sup>‡,||,⊥</sup> and Roman Sordan<sup>\*,†</sup>

<sup>†</sup>L-NESS, Department of Physics, Politecnico di Milano, Polo di Como, Via Anzani 42, 22100 Como, Italy

<sup>‡</sup>Department of Electrical and Computer Engineering, University of Illinois at Urbana–Champaign, Urbana, Illinois 61801, United States

<sup>§</sup>Department of Science and High Technology, Universitá degli Studi dell'Insubria, Via Valleggio 11, 22100 Como, Italy <sup>II</sup>Micro and Nanotechnology Lab, University of Illinois at Urbana–Champaign, Urbana, Illinois 61801, United States <sup>L</sup>Beckman Institute, University of Illinois at Urbana–Champaign, Urbana, Illinois 61801, United States

**(5)** Supporting Information

**ABSTRACT:** The fundamental building blocks of digital electronics are logic gates which must be capable of cascading such that more complex logic functions can be realized. Here we demonstrate integrated graphene complementary inverters which operate with the same input and output voltage logic levels, thus allowing cascading. We obtain signal matching under ambient conditions with inverters fabricated from wafer-scale graphene grown by chemical vapor deposition (CVD). Monolayer graphene was incorporated in self-aligned field-effect transistors in which the top gate overlaps with the source

and drain contacts. This results in full-channel gating and leads to the highest low-frequency voltage gain reported so far in topgated CVD graphene devices operating in air ambient,  $A_v \sim -5$ . Such gain enabled logic inverters with the same voltage swing of 0.56 V at their input and output. Graphene inverters could find their way in realistic applications where high-speed operation is desired but power dissipation is not a concern, similar to emitter-coupled logic.

KEYWORDS: Graphene, integrated circuit, logic gates, voltage gain, digital electronics

T he high mobility of charge carriers in graphene<sup>1</sup> at room temperature<sup>2-4</sup> makes this two-dimensional material attractive for applications in high-speed electronics.<sup>5,6</sup> However, graphene field-effect transistors (FETs) must exhibit intrinsic voltage gain  $A = g_m/g_d > 1$  in order to be useful in practical electronic applications, where  $g_m$  is transconductance and  $g_d$  is output conductance. The intrinsic voltage gain of such FETs is limited by the zero bandgap of graphene which prevents depletion of charge carriers. This limits the control of gate voltage over the drain current; i.e., it reduces the transconductance g<sub>m</sub> with respect to conventional semiconductor FETs which can be turned off at suitable gate biases.<sup>7</sup> Lack of depletion also leads to a weaker drain current saturation regime in graphene FETs, which in turn increases their output conductance g<sub>d</sub>. Hence, most graphene FETs fabricated so far have intrinsic gain smaller than unity,<sup>8–14</sup> preventing the realization of analogue voltage amplifiers and digital logic gates which are the main building blocks of analogue and digital electronics, respectively. Without voltage gain, the use of graphene FETs is limited to niche applications such as analogue mixers,<sup>15</sup> but even these require voltage amplifiers for signal processing. Recent reports of over-unity voltage gain in graphene FETs at room temperature  $^{16-18}$  pave the way for

the use of graphene FETs in analogue electronics. However, such voltage gain has not been utilized so far in digital logic gates at room temperature in which high gain is required in order to match input and output digital signals. Without in/out digital signal matching logic gates cannot be cascaded, and thus realistic digital circuits cannot be realized. Signal matching in graphene inverters has only been reported so far at cryogenic temperatures in exfoliated graphene samples.<sup>19,20</sup>

In this work we demonstrate the highest low-frequency voltage gain obtained so far in wafer-scale graphene integrated circuits under ambient conditions. This voltage gain arises from the large intrinsic gain of the graphene FETs which were integrated into digital complementary inverters. In contrast to other graphene FET implementations in which there were ungated parts of channel on either side of the gate,<sup>21</sup> the FETs described here do not have these ungated parts of the channel due to a self-aligned top-gate fabrication process.<sup>17</sup> Such a scheme results in higher transconductance ( $g_m \sim 150 \ \mu S/\mu m$ ) in the fabricated FETs, comparable to that obtained in

Received:

March 20, 2012

Revised:

June 6, 2012

Published:

July 13, 2012

#### **Nano Letters**

exfoliated graphene FETs deposited on exfoliated hexagonal-BN (h-BN) flakes, which is not a scalable technology.<sup>22</sup> Our top-gated approach also screens the charge traps surrounding the channel and eliminates hysteresis in the transfer curves of the fabricated FETs, which in the past has been detrimental to the stability of graphene devices operating at room temperature.<sup>20,23</sup> In this way we have realized the first integrated wafer-scale graphene logic gates operating with digital signal matching in air ambient at room temperature. We also demonstrate cascading of digital graphene inverters with the previous stage capable of triggering the next stage, which has not been demonstrated so far at any temperature. The combination of transistor properties along with the use of very thin gate insulators employed here results in voltage gains that can be utilized in a large variety of electronic circuits, including analogue voltage amplifiers and digital logic gates.

Integrated graphene complementary inverters were fabricated from graphene monolayers (see Methods section and Supporting Information Figure S1) grown by chemical-vapor deposition (CVD) on Cu with a CH<sub>4</sub> precursor<sup>24</sup> and then transferred to conventional SiO<sub>2</sub>(300 nm)/Si substrates. Al gate electrodes were fabricated by direct evaporation of Al on graphene. A very thin ( $\sim 4$  nm) gate insulator (AlO<sub>x</sub>) was naturally formed at the interface between the Al gate and graphene by exposing the samples to air.<sup>19</sup> The source and drain contacts (Ti/Au) fabricated in the following step were slightly overlapped with the gate contact in order to completely cover the source-drain channel with the  $AlO_r/Al$  gate stack. This maximizes the gate voltage control over the drain current because there are no ungated parts of the channel to add access resistances and reduce the intrinsic voltage gain. As the gate fully covers the channel, the graphene is partially screened from water charge traps adsorbed on the substrate<sup>13,25</sup> such that gate hysteresis is suppressed.<sup>26</sup> The gate also serves as an additional heat sink allowing high drain currents<sup>27</sup> and consequently higher voltage gain. This also reduces the influence of atmospheric contaminants during high-current operation<sup>9,28</sup> such that the electrical properties of the FETs are stable. The AlO<sub>x</sub> layer which forms on the surface of the Al gate prevents short circuits between the top gate and the source/drain contacts (despite overlap, gate leakage was found to be negligible; see Methods section).

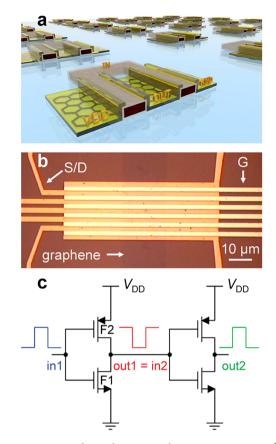

A schematic of the investigated complementary inverters is shown in Figure 1. As fabricated, both FETs F1 and F2 in each inverter are identical. Examined channel lengths were L = 1 or 2  $\mu$ m, and other dimensions and details are given in the Methods section. The two FETs change into complementary types (F2 into p-type and F1 into n-type) after the supply voltage  $V_{DD} > 0$ is applied.<sup>19</sup> Under bias, the potential of the graphene channel in F2 increases with respect to that of F1, which therefore shifts the Dirac point of F2 to higher input voltages. Complementary operation is obtained between the Dirac points of the two FETs.<sup>9</sup> The highest voltage gain is reached at the direct-current (DC) operating point that lies approximately halfway between the Dirac points of the two FETs.<sup>9,17,19,20</sup> For this reason, the DC components of the input and output voltages at the highest-gain point in inverters biased with negligibly small  $V_{\rm DD}$ are  $V_{\rm IN} = V_0$  and  $V_{\rm OUT} = 0$ , where  $V_0$  is the voltage at the Dirac point of the unbiased FETs. As the supply voltage  $V_{DD}$  is increased, these two DC components shift by  $V_{\rm DD}/(1 + \alpha)$  to  $V_{\rm IN} \approx V_0 + V_{\rm DD}/(1 + \alpha)$  and  $V_{\rm OUT} = V_{\rm DD}/(1 + \alpha)$  due to circuit symmetry. Here  $\alpha$  is the ratio of transistor resistances at  $V_{\rm IN} = 0$  (typically  $\alpha = 1$ ).<sup>9</sup> Hence,  $V_{\rm IN} - V_{\rm OUT} = V_0$  represents a

**Figure 1.** Integrated graphene complementary inverters. (a) A schematic of a large array of inverters fabricated on wafer-scale graphene. Source ( $V_{DD}$ , GND) and drain (OUT) contacts (Ti/Au; yellow) overlap with gate (IN) contacts (Al; red core) covered by an insulating layer (AlO<sub>x</sub>; gray shell). (b) An optical microscope image of three inverters integrated on the same monolayer graphene channel grown by CVD. The arrows indicate source (S), drain (D), gate (G), and graphene channel. (c) A circuit diagram of two cascaded inverters. The output (out1) of the first inverter (comprised of FETs F1 and F2) is connected to the input (in2) of the second inverter. The test results of cascading two such inverters are shown in Figure 4.

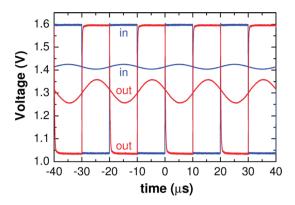

mismatch between the DC components of the input and output voltages at the highest-gain point. This is illustrated in Figure 2, which shows measured alternating current (AC) input and output signals of an inverter biased at the highest-gain point for  $V_{\rm DD} = 2.5$  V. The signals are offset by  $V_0 \approx 0.11$  V. A positive voltage  $V_0$  at the Dirac point was found in all fabricated FETs in air (see Figure S2), and it stems from p-type doping introduced by ambient impurities adsorbed on graphene prior to fabrication.<sup>1,29</sup> In addition, we note that  $V_0$  is stable in air at room temperature without hysteresis present,<sup>26</sup> which confirms the good quality of the devices and the protective effect of the top gate.

In the complementary configuration, the DC voltage gain  $A_{v,DC} = dV_{OUT}/dV_{IN}$  of an inverter is equal to the intrinsic gain of a single FET,<sup>17</sup> i.e.,  $A_{v,DC} = -A$ . The low-frequency small-signal AC voltage gain  $A_v = v_{out}/v_{in}$  was found to be identical to the DC voltage gain, thus demonstrating suppression of the hysteretic behavior of the graphene FETs in air.<sup>17</sup> Here  $v_{in}$  and  $v_{out}$  are AC components of the input and output voltage signals, respectively. The largest value of the AC voltage gain in air was found to be  $A_v = -5.3$  at  $V_{DD} = 2.5$  V (see Figure S4). Overunity voltage gain is a prerequisite for signal matching;

**Figure 2.** Analogue and digital waveforms measured at the input and output of a typical graphene inverter under ambient conditions at a voltage supply  $V_{\rm DD} = 2.5$  V and frequency f = 50 kHz. Sine waveform signals were measured at the highest-gain point at which there is a mismatch of  $V_0 = 0.11$  V between the DC components of the signals. The amplitude of the output sine wave is 4.7 times larger than the amplitude of the input sine wave; hence  $A_v = -4.7$ . Digital waveforms were measured at the DC operating point at which there is no in/out DC signal mismatch. The largest input voltage swing  $V_{\rm in,p-p} = 0.56$  V at which the signals are matched is used. The digital voltage swing is slightly less than in the case when the inverters are operated at the highest gain point ( $V_{\rm in,p-p} = 0.60$  V, see Figure S10).

otherwise, the voltage swing at the output is smaller than at the input. The good voltage gain is obtained here in the fabricated FETs due to a combination of factors including full-channel gating, thin gate oxide (leading to good control of the top-gate over the channel), good mobility, low output conductance, and manageable contact resistance (for the  $\sim 1 \mu m$  channel lengths explored here). Nevertheless, we note that all of the above can continue to be optimized, yielding further improvements of graphene inverters and amplifiers in future work.

In particular, the top-gated approach employed here results in good transconductance  $g_{\rm m} \sim 3~{\rm mS}~(150~{\mu {\rm S}}/{\mu {\rm m}})$  and relatively low output conductance  $g_d \sim 1 \text{ mS} (50 \ \mu\text{S}/\mu\text{m})$ under operating conditions, which leads to  $A \sim 3$  (see Figure S5). The obtained transconductance is comparable to that measured in exfoliated graphene FETs deposited on very smooth exfoliated h-BN flakes<sup>22</sup> due to the elimination of access resistances through the self-aligned fabrication process.<sup>17</sup> The intrinsic carrier mobility is  $\mu_{in} \sim 1000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  after extraction of contact resistance (see Figure S6), which is comparable to carrier mobilities obtained in similar exfoliated top-gated FETs.<sup>19,22</sup> The voltage gain  $A_v$  is larger than the intrinsic gain A as the former is measured in an inverter configuration in which the contact resistance of the common drain (i.e., integrated output, see Figure 1) does not influence the measurements. This is because the output of the inverter is loaded with a very large input resistance of a voltmeter, oscilloscope, or next inverter stage. The voltage gain obtained in this work is larger than that of -1.7 recently demonstrated in CVD-grown graphene incorporating interdigitated FETs<sup>16</sup> and also larger than -3.7 obtained in exfoliated samples incorporating FETs similar to those investigated here.<sup>17</sup>

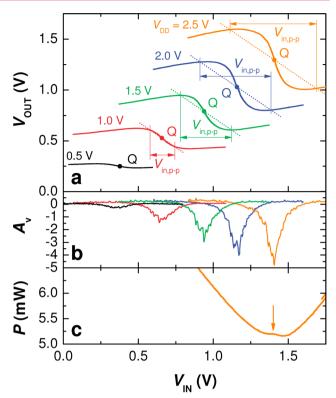

Measurements were performed on inverters in which the Dirac point was close to zero ( $V_0 < 0.2$  V) and which were stable operating with matched signals in air ambient (we have also measured a few devices with initial  $V_0 > 0.2$  V, which required some vacuum exposure to reduce  $V_0$ ; see Figures S7–S9 and surrounding text). Figure 3a shows the DC transfer

**Figure 3.** DC characteristics of a graphene inverter under ambient conditions. (a) Transfer curves of an inverter at different supply voltages. The highest-gain point at each supply voltage is denoted by Q. The maximum input voltage swing  $V_{in,p-p}$  at which input and output signals are matched ( $V_{out,p-p} = V_{in,p-p}$ ) is determined by the intersections between the transfer curve and a unity gain line (slope of -1) passing through Q. (b) DC voltage gain  $A_v$  of the same inverter at different supply voltages. (c) Power dissipation of the same graphene inverter at  $V_{DD} = 2.5$  V. The arrow represents the local maximum of dissipated power at the Q point (see (a) and text), similar to Si inverter technology.

curves  $V_{\rm OUT}$  vs  $V_{\rm IN}$  of one of the inverters at different supply voltages  $V_{\rm DD}$ . The voltage gain increases at greater supply voltages<sup>20,17</sup> and the largest value under ambient conditions was typically found to be  $A_v \sim -5$  at  $V_{DD} = 2.5$  V (Figure 3b). The highest-gain operating point Q is located at  $V_{\rm IN} \approx V_{\rm OUT}$ which allows in/out signals to be matched. As digital signals must have two well distinguished logic states (Boolean 0 and 1) the voltage gain must be >1 if peak-to-peak values (or swing) of the input  $(V_{in,p-p})$  and output  $(V_{out,p-p})$  digital voltage signals are to be the same. The maximum swing  $V_{in,p-p}$  at which  $V_{\text{out,p-p}} = V_{\text{in,p-p}}$  can be determined from the intersection between the transfer curve and a unity-gain line passing through the highest-gain point Q (Figure 3). This exemplifies the importance of a large voltage gain a Q (i.e., large supply  $V_{\rm DD}$ ), as when this is not satisfied<sup>23</sup>  $V_{\rm in,p-p}$  is too small to be reliably detected (i.e., it is below the thermal voltage  $V_{\rm T} = k_{\rm B}T/$ e, where  $k_{\rm B}$  is the Boltzmann constant, T temperature, and e elementary charge). In addition, if devices with  $V_0 > 0.2$  V are used, then biasing inverters away from the highest-gain point Q in order to match in/out signals rapidly reduces the swing  $V_{\text{in,p-p}}$  (see Figure S7).

Figure 3c shows power dissipation of an inverter as a function of the input voltage. At the highest-gain point Q there is a small local maximum (marked by an arrow) of the dissipated power. In conventional Si inverters this is a global

maximum of power,<sup>30</sup> and the power reduces to zero on either side of the operating point Q as Si inverters approach rail-to-rail operation, which eliminates static dissipation. The power dissipated by the graphene inverters also decreases on either side of the point Q, but it does not reach zero; instead, the minima are at  $\approx$ 98% of the local maximum, and thus graphene inverters dissipate power regardless of the position of the operating point. At larger input voltage swings, the power increases as the operating point exits the area between the Dirac points of the FETs and enters the area in which both FETs are highly conductive. The power dissipation could be lowered by reducing the supply voltage  $V_{DD}$ . However, this also reduces the voltage gain and consequently  $V_{in,p-p}$ . Nevertheless, such graphene inverters could find uses in applications not suitable for traditional Si logic, such as transparent circuits on flexible substrates, or ultrafast logic applications where power dissipation is not a concern, further discussed below.

Figure 2 also shows input and output digital voltage signals of an inverter biased with  $V_{DD} = 2.5$  V at an input signal frequency f = 50 kHz. The output signal takes the same logic voltage levels as the input signal, thus allowing inverters to be cascaded which is a key prerequisite in digital electronics. At this supply voltage, the maximum in/out voltage swing is  $V_{\text{out,p-p}} = V_{\text{in,p-p}} = 0.56 \text{ V}$  or nearly 22 times the thermal voltage  $V_{\text{T}}$ , which is large enough for logic states to be unambiguously resolved from one another by the next logic gate. However, graphene FETs cannot be turned off in either of the two logic states, and the in/out voltage swing is only ~22.4% of the supply voltage. Although this is less than the voltage swing in traditional (e.g., Si-based) complementary metal oxide semiconductor (CMOS) logic (capable of rail-to-rail operation with the voltage swing reaching almost 100% of the supply voltage),<sup>30</sup> it is still more than the swing in emitter coupled logic (ECL) gates, the fastest logic family.<sup>30</sup> Similar to graphene logic gates, ECL gates are also comprised of overdriven transistors in order to achieve ultrafast operation. For this reason a typical swing of the ECL gates is 0.8 V at a supply of 5.2 V, i.e., only 15% of the supply voltage.<sup>30</sup> Static power consumption of a standard ECL gate is ~10 mW, similar to the consumption of the graphene logic gates. ECL gates are at the core of the fastest SiGe bipolar-CMOS (BiCMOS) or InP heterojunction bipolar transistor (HBT) chips and are used for digital signal processing at extremely high frequencies (EHFs; f > 100 GHz) which are inaccessible with conventional state-of-the-art CMOS technology. For example, they are used in high-speed integer arithmetic units,<sup>31</sup> static EHF dividers,<sup>32</sup> high data rate (>50 Gb/s) serial communication systems for demultiplexing,<sup>33</sup> and phase detection for clock and data signal recovery.<sup>34,35</sup>

Graphene logic gates are expected to offer several advantages over state-of-the-art ECL gates. They are simpler to fabricate than ECL gates as the latter are comprised of complex HBTs. Graphene also has higher charge carrier mobility compared to that of SiGe and InP, which opens a route to higher operating frequencies. Finally, graphene logic is not expected to be constrained by a tradeoff between the highest operating frequency and the breakdown voltage, which represents a serious limitation of HBTs.<sup>36</sup> However, there are also several technological challenges that must be overcome before graphene FETs could replace HBTs in ECL-like logic. Contact resistance of graphene FETs must be reduced to <10  $\Omega \cdot \mu m$  in order to fully exploit the high intrinsic carrier mobility in graphene.<sup>37,38</sup> Graphene FETs are yet to exhibit over-unity voltage gain in the EHF range—the widest reported bandwidth of graphene voltage amplifiers is 6 GHz.<sup>16</sup> Finally, HBT technology provides a simple and flexible route to applicationtailored transistors via bandgap engineering. Conversely, bandgap engineering in graphene is mostly limited to patterning graphene into nanoribbons,<sup>39,40</sup> which despite the demonstration of several nanoelectronic prototypes<sup>13,27,41-45</sup> has not yet produced FETs with A > 1.

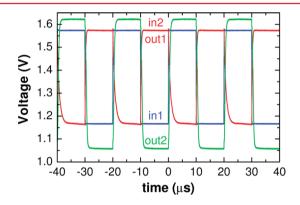

Demonstration of in/out signal matching does not necessarily imply successful cascading of graphene inverters in realistic applications. Because of remaining fabrication challenges of graphene, two randomly selected inverters usually do not have identical transfer characteristics, i.e., their highestgain operating points Q1 and Q2 are not the same. As a consequence, it is not possible to bias two inverters such that both of them operate at their highest-gain points. However, we found that a mismatch in the positions of the highest gain points can be compensated if the gain of the inverters is large enough (typically  $|A_v| > 3$ ), which leads to successful cascading. Figure 4 shows input and output voltage signals of two

**Figure 4.** Digital waveforms measured under ambient conditions in a cascade connection of two graphene inverters (connected as in Figure 1c). The supply voltage is  $V_{\rm DD}$  = 2.5 V and frequency f = 50 kHz. Transient behavior observed in this plot (see also Figure S14) is a consequence of the limited bandwidth of the used equipment (see Figure S13), as discussed in the Methods section.

inverters, where the first inverter (1) clocks the second one (2); i.e., the output of inverter 1 is connected to the input of inverter 2 as shown in Figure 1c. The signal matching in Figure 4 was obtained at the DC operating point which lies between the highest-gain points Q1 and Q2 of the two inverters. As both inverters exhibit high gain (here  $|A_v| > 4$ ) at their points Q1 and Q2, they preserve the over-unity voltage gain between these two points, and consequently the gain was maintained on making the cascade connection, resulting in the same logic states 0 and 1 of all signals shown in Figure 4. The final low (high) logic state is correctly interpreted as 0 (1) because its voltage level is below (above) the voltage level of the same state at the input. Such small mismatches between the voltage levels in graphene inverters are expected because the saturation voltage levels in graphene inverters are not well-defined (in contrast to CMOS inverters in which saturation levels are unambiguously defined by ground and  $V_{DD}$ ). However, this does not influence operation of the cascaded graphene logic gates, as high gain prevents the appearance of intermediate voltage levels (between the high and low levels set by the input) during the propagation of the digital signal.

In summary, we have demonstrated integrated graphene complementary inverters with matched input and output digital signals in room temperature, air-ambient conditions. We have also successfully cascaded graphene logic gates into more complex logic circuits. We realized signal matching with the highest AC voltage gain of  $\sim -5$  reported to date in top-gated graphene FETs from wafer-scale CVD growth. These achievements suggest opportunities for graphene<sup>46</sup> as ultrafast logic gates in scenarios where static power dissipation is not a concern, similar to ECL logic; our graphene logic gates already have larger voltage swing (as a fraction of supply voltage) than ECL gates, and this could be improved through further advances. Importantly, our study has also served to highlight several remaining challenges of graphene FETs, most technological rather than fundamental in nature. For instance, graphene circuits remain sensitive to fabrication-induced variability, but we show that this does not influence the operation of graphene logic gates as long as the graphene FETs exhibit high voltage gain. Finally, achieving higher transconductance  $(g_m)$ , lower output conductance  $(g_d)$ , and lower contact resistance will all continue to increase the voltage gain for both analog and digital applications.

Methods. The devices were patterned by electron-beam lithography and reactive-ion etching, while the contacts were deposited in an electron-beam evaporator. Source and drain contacts consisted of Ti/Au (5/35 nm or 2/35 nm) while gate was made of Al (90 nm). FETs with thinner Ti adhesion layers exhibited lower contact resistances and thus higher voltage gain. A ~4 nm thin gate insulator  $(AlO_x)$  was naturally formed at the surfaces of Al by exposing the samples to air.<sup>19,20</sup> Under operating conditions the gate current I<sub>G</sub> was found to be less than 1 nA, i.e., at least 6 orders of magnitude smaller than the drain current  $I_{\rm D}$  (see Figures S11 and S12). Gate oxide breakdown occurred at gate voltages  $V_{\rm G}$  > 3 V. After breakdown the resistance between the gate and source/drain contacts was reduced to ~100  $\Omega$ . However, in contrast to previous reports,<sup>19,20</sup> the breakdown was found to be irreversible, probably indicating damage in the overlap area between the contacts. The FET channel dimensions were length  $L = 2 \ \mu m$  and width  $W = 20 \ \mu m$ . Apart from these, several devices with  $L = 1 \ \mu m$  and 500 nm were also fabricated. The voltage gain was found to be independent of L, which was expected as  $g_m$  and  $g_d$  both scale with W/L.<sup>20,17</sup> All measurements were performed at room temperature in air with the Si substrate grounded. The DC characteristics were measured using Keithley source meters (2611) and multimeters (2000) controlled by a custom-built LabView routine. The waveform measurements were performed by applying input voltages from a Tektronix AFG 3022B function generator while input and output signals were measured by an Agilent Infiniium DSO9064A digital storage oscilloscope. Although fabricated devices have intrinsic unity-gain frequency of ~9 GHz,<sup>17</sup> the waveform measurements were performed at f = 50 kHz because the bandwidth of the used measurement setup was limited by the output resistance of the inverters (~1 k $\Omega$ ) and parasitic capacitance of the cables (~0.6 nF) to ~270 kHz (see Figure S13). Measurements performed at higher frequencies are shown in Figure S14.

## ASSOCIATED CONTENT

#### **Supporting Information**

Measurements and discussions on Raman spectrum of monolayer graphene, statistics on the fabricated graphene FETs, transfer curves of the typical graphene FETs, AC signals demonstrating voltage gain  $A_v = -5.3$ , typical small-signal

parameters of the fabricated FETs in air, statistics on the extrinsic mobility of the fabricated graphene FETs, waveforms measured in samples with larger Dirac voltages at a low pressure, digital waveforms measured in air at the highest-gain point, comparison between drain and gate currents under operating conditions, frequency response of the inverters, and digital waveforms measured at higher frequencies. This material is available free of charge via the Internet at http://pubs.acs.org.

# AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: roman.sordan@como.polimi.it.

#### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

This research was supported in part by Directa Plus srl and Fondazione Cariplo, Grant No. 2011-0373, and by the United States Office of Naval Research (ONR) and Air Force Office of Scientific Research (AFOSR). We thank S. Masci for technical support.

# REFERENCES

(1) Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. *Science* **2004**, *306*, 666–669.

(2) Hong, X.; Posadas, A.; Zou, K.; Ahn, C. H.; Zhu, J. Phys. Rev. Lett. 2009, 102, 136808.

(3) Dean, C. R.; Young, A. F.; Meric, I.; Lee, C.; Wang, L.; Sorgenfrei, S.; Watanabe, K.; Taniguchi, T.; Kim, P.; Shepard, K. L.; Hone, J. *Nat. Nanotechnol.* **2010**, *5*, 722–726.

- (4) Dorgan, V. E.; Bae, M.-H.; Pop, E. Appl. Phys. Lett. 2010, 97, 082112.

- (5) Lin, Y.-M.; Dimitrakopoulos, C.; Jenkins, K. A.; Farmer, D. B.; Chiu, H.-Y.; Grill, A.; Avouris, P. *Science* **2010**, *327*, 662.

- (6) Liao, L.; Bai, J.; Cheng, R.; Zhou, H.; Liu, L.; Liu, Y.; Huang, Y.; Duan, X. Nano Lett. 2012, 12, 2653–2657.

- (7) Sze, S. M. Physics of Semiconductor Devices; Wiley-Interscience: New York, 1981.

- (8) Sordan, R.; Traversi, F.; Russo, V. Appl. Phys. Lett. 2009, 94, 073305.

- (9) Traversi, F.; Russo, V.; Sordan, R. Appl. Phys. Lett. 2009, 94, 223312.

- (10) Wang, H.; Nezich, D.; Kong, J.; Palacios, T. *IEEE Electron Device Lett.* **2009**, 30, 547–549.

- (11) Harada, N.; Yagi, K.; Sato, S.; Yokoyama, N. Appl. Phys. Lett. 2010, 96, 012102.

- (12) Yang, X.; Liu, G.; Balandin, A. A.; Mohanram, K. ACS Nano 2010, 4, 5532-5538.

- (13) Stützel, E. U.; Burghard, M.; Kern, K.; Traversi, F.; Nichele, F.; Sordan, R. *Small* **2010**, *6*, 2822–2825.

- (14) Yang, X.; Liu, G.; Rostami, M.; Balandin, A. A.; Mohanram, K. *IEEE Electron Device Lett.* **2011**, *32*, 1328–1330.

- (15) Hsu, A.; Wang, H.; Wu, J.; Kong, J.; Palacios, T. *IEEE Electron Device Lett.* **2010**, *31*, 906–908.

- (16) Han, S.-J.; Jenkins, K. A.; Garcia, A. V.; Franklin, A. D.; Bol, A. A.; Haensch, W. *Nano Lett.* **2011**, *11*, 3690–3693.

- (17) Guerriero, E.; Polloni, L.; Rizzi, L. G.; Bianchi, M.; Mondello, G.; Sordan, R. *Small* **2012**, *8*, 357–361.

- (18) Szafranek, B. N.; Fiori, G.; Schall, D.; Neumaier, D.; Kurz, H. Nano Lett. **2012**, *12*, 1324–1328.

- (19) Li, S.-L.; Miyazaki, H.; Kumatani, A.; Kanda, A.; Tsukagoshi, K. Nano Lett. **2010**, *10*, 2357–2362.

(20) Li, S.-L.; Miyazaki, H.; Hiura, H.; Liu, C.; Tsukagoshi, K. ACS Nano 2011, 5, 500–506.

(21) Schwierz, F. Nat. Nanotechnol. 2010, 5, 487-496.

(22) Wang, H.; Taychatanapat, T.; Hsu, A.; Watanabe, K.; Taniguchi, T.; Jarillo-Herrero, P.; Palacios, T. *IEEE Electron Device Lett.* **2011**, *32*, 1209–1211.

(23) Sagar, A.; Balasubramanian, K.; Burghard, M.; Kern, K.; Sordan, R. *Appl. Phys. Lett.* **2011**, *99*, 043307.

(24) Wood, J. D.; Schmucker, S. W.; Lyons, A. S.; Pop, E.; Lyding, J. W. Nano Lett. **2011**, *11*, 4547–4554.

(25) Kim, W.; Javey, A.; Vermesh, O.; Wang, Q.; Li, Y.; Dai, H. Nano Lett. 2003, 3, 193–198.

(26) Estrada, D.; Dutta, S.; Liao, A.; Pop, E. *Nanotechnology* **2010**, *21*, 085702.

(27) Liao, A. D.; Wu, J. Z.; Wang, X.; Tahy, K.; Jena, D.; Dai, H.; Pop, E. *Phys. Rev. Lett.* **2011**, *106*, 256801.

(28) Moser, J.; Barreiro, A.; Bachtold, A. Appl. Phys. Lett. 2007, 91, 163513.

(29) Liu, L.; Ryu, S.; Tomasik, M. R.; Stolyarova, E.; Jung, N.; Hybertsen, M. S.; Steigerwald, M. L.; Brus, L. E.; Flynn, G. W. *Nano Lett.* **2008**, 8, 1965–1970.

(30) Ayers, J. E. Digital Integrated Circuits: Analysis and Design; CRC Press: Boca Raton, FL, 2009.

(31) Gutin, A.; Jacob, P.; Chu, M.; Belemjian, P.; LeRoy, M.; Kraft, R.; McDonald, J. *IEEE T. Circuits Syst.* **2011**, *58*, 2201–2210.

(32) Knapp, H.; Meister, T.; Liebl, W.; Claeys, D.; Popp, T.; Aufinger, K.; Schäfer, H.; Böck, J.; Boguth, S.; Lachner, R. *IEEE Bipolar/BiCMOS Circuits Technol. Meet.* **2010**, 29–32.

(33) Konczykowska, A.; Jorge, F.; Dupuy, J.-Y.; Riet, M.; Godin, J.; Scavennec, A.; Bach, H.-G.; Mekonnen, G. G.; Pech, D.; Schubert, C. 18th Int. Conf. Microwave Radar Wireless Commun. (MIKON) 2010, 1–4.

(34) Joram, N.; Barghouthi, A.; Knochenhauer, C.; Ellinger, F.; Scheytt, C. Semicond. Conf. Dresden (SCD) 2011, 1–4.

(35) Joram, N.; Barghouthi, A.; Knochenhauer, C.; Ellinger, F.; Scheytt, C. IEEE MTT-S Int. Microwave Symp. Digest (MTT) 2011, 1–4.

(36) Cressler, J. D.; Niu, G. Silicon-Germanium Heterojunction Bipolar Transistors; Artech House Publishers: Boston, 2003.

(37) Nagashio, K.; Nishimura, T.; Kita, K.; Toriumi, A. Appl. Phys. Lett. 2010, 97, 143514.

(38) Nagashio, K.; Toriumi, A. Jpn. J. Appl. Phys. 2011, 50, 070108.

(39) Barone, V.; Hod, O.; Scuseria, G. E. Nano Lett. 2006, 6, 2748–2754.

(40) Son, Y.-W.; Cohen, M. L.; Louie, S. G. Phys. Rev. Lett. 2006, 97, 216803.

(41) Han, M. Y.; Özyilmaz, B.; Zhang, Y.; Kim, P. Phys. Rev. Lett. 2007, 98, 206805.

(42) Li, X.; Wang, X.; Zhang, L.; Lee, S.; Dai, H. Science 2008, 319, 1229–1232.

(43) Wang, X.; Ouyang, Y.; Li, X.; Wang, H.; Guo, J.; Dai, H. Phys. Rev. Lett. 2008, 100, 206803.

(44) Liao, L.; Bai, J.; Lin, Y.-C.; Qu, Y.; Huang, Y.; Duan, X. Adv. Mater. **2010**, 22, 1941–1945.

(45) Liao, L.; Bai, J.; Cheng, R.; Lin, Y.-C.; Jiang, S.; Huang, Y.; Duan, X. Nano Lett. **2010**, 10, 1917–1921.

(46) Pasanen, P.; Voutilainen, M.; Helle, M.; Song, X.; Hakonen, P. J. *Phys. Scr.* **2012**, 2012, 014025.

#### NOTE ADDED AFTER ASAP PUBLICATION

This paper was published ASAP on July 13, 2012. Reference 18 has been updated. The revised version was posted on August 8, 2012.