# **OPEN**

Received: 10 November 2016 Accepted: 12 April 2017 Published online: 25 May 2017

# High-Gain Graphene Transistors with a Thin AlOx Top-Gate Oxide

Erica Guerriero 1, Paolo Pedrinazzi 1, Aida Mansouri 1, Omid Habibpour 1, Michael Winters 2, Niklas Rorsman 2, Ashkan Behnam 3, Enrique A. Carrion 3, Amaia Pesquera 4, Alba Centeno 4, Amaia Zurutuza 4, Eric Pop 5, Herbert Zirath 2 & Roman Sordan 1

The high-frequency performance of transistors is usually assessed by speed and gain figures of merit, such as the maximum oscillation frequency  $f_{\rm max}$ , cutoff frequency  $f_{\rm T}$ , ratio  $f_{\rm max}/f_{\rm T}$ , forward transmission coefficient  $S_{21}$ , and open-circuit voltage gain  $A_{\rm v}$ . All these figures of merit must be as large as possible for transistors to be useful in practical electronics applications. Here we demonstrate high-performance graphene field-effect transistors (GFETs) with a thin AlOx gate dielectric which outperform previous state-of-the-art GFETs: we obtained  $f_{\rm max}/f_{\rm T} > 3$ ,  $A_{\rm v} > 30\,{\rm dB}$ , and  $S_{21} = 12.5\,{\rm dB}$  (at 10 MHz and depending on the transistor geometry) from S-parameter measurements. A dc characterization of GFETs in ambient conditions reveals good current saturation and relatively large transconductance ~600 S/m. The realized GFETs offer the prospect of using graphene in a much wider range of electronic applications which require substantial gain.

Graphene is one of the most intensively investigated two-dimensional materials for electronics owing to its large charge carrier mobility  $(>5,000 \, \text{cm}^2/(\text{Vs})$  at room temperature)<sup>1</sup>, which is almost equal between holes and electrons<sup>2</sup>, and large saturation velocity<sup>3</sup>. However, despite intensive research efforts, there are no graphene-based electronic devices available on the market at present. The lack of a bandgap in graphene prevents GFETs from being turned off, which results in large off-state currents and high static power dissipation, and thus represents a fundamental obstacle for the development of graphene-based logic gates<sup>4</sup>.

In contrast, turning off transistors is not required for most analog applications, but the absence of a bandgap weakens the drain current saturation required for high gain operation. Therefore, improving current saturation in GFETs in combination with high mobility of graphene, represent a promising path in the field of high-frequency analog electronics. One possible way to improve current saturation in GFETs is to use ultra-clean samples exhibiting high saturation velocity on substrates with high phonon energy and small density of defects, e.g., h-BN $^5$ . However, this technology is not yet mature enough to be applied in a large-scale production and is limited by the high cost and complex processing. Similarly, patterning graphene into nanoribbons to open a bandgap reduces the charge carrier mobility and therefore the on-state current, eliminating advantage of improved current saturation. A different approach consists of using thin gate dielectrics in order to assist the channel "pinch-off" and reduce the effect of intrinsic carriers and interfacial traps, which consistently improves saturation  $^6$ . A thinner oxide (thickness  $t_{ox}$ ) also improves the transconductance ( $t_{ox}$ ) which is proportional to  $t_{ox}$ .

Here we demonstrate high-frequency GFETs on conventional SiO<sub>2</sub> substrates with improved drain current saturation yielding high-gain operation. The current saturation was improved by utilizing a thin  $(t_{ox} \sim 4 \text{ nm})$  AlO<sub>x</sub> top-gate insulator with good dielectric constant  $(\varepsilon_{r,ox} \sim 6.4)$ . This resulted in improved oxide capacitance  $(C_{ox} = 1.37 \, \mu\text{F/cm}^2)^{7.8}$  and therefore strong gate control over carriers in the graphene channel. As a consequence, the output conductance  $(g_d)$  was reduced well below 50 S/m (normalized by the channel width W) leading to very large values of the open-circuit voltage gain  $A_v > 30 \, \text{dB}$  and forward gain  $S_{21} = 12.5 \, \text{dB}$  (at 10 MHz) in GFETs with the channel widths  $W = 10 \, \mu\text{m}$  and  $W = 100 \, \mu\text{m}$ , respectively, which are the highest gains measured in GFETs so far<sup>9-12</sup>. This low output conductance also contributed to a large ratio between the extrinsic maximum oscillation frequency  $(f_{max})$  and cutoff frequency  $(f_T)$  of  $\sim 3$ , which is unusually high for GFETs, in which  $f_{max}/f_T$  typically

<sup>1</sup>L-NESS, Department of Physics, Politecnico di Milano, Polo di Como, Via Anzani 42, 22100, Como, Italy. Department of Microtechnology and Nanoscience, Chalmers University of Technology, Gothenburg, 41296, Sweden. Department of Electrical and Computer Engineering, University of Illinois, Urbana, IL, 61801, USA. Graphenea, Avenida de Tolosa 76, 20018, Donostia/San Sebastián, Spain. Department of Electrical Engineering, Stanford University, Stanford, CA, 94305, USA. Erica Guerriero and Paolo Pedrinazzi contributed equally to this work. Correspondence and requests for materials should be addressed to R.S. (email: roman.sordan@polimi.it)

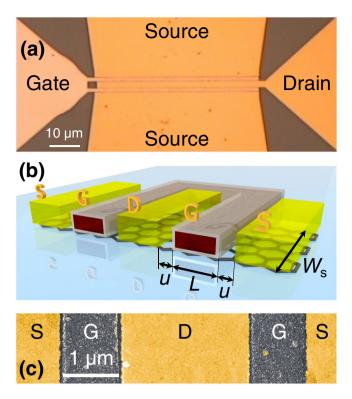

**Figure 1.** High-frequency GFET. (a) Optical image of one of the fabricated GFETs with the gate length  $L=1.1~\mu\mathrm{m}$ . Graphene stripe cannot be seen as it is completely covered by the contacts. (b) Schematic of the central part of the GFET. Source (S) and drain (D) contacts (Au; yellow) are separated by an underlap (length u) from the gate (G) contact (Al; red core), which is covered by an insulating layer (AlOx; gray shell). Width of graphene stripes  $W_s$  was 5, 20 and 50  $\mu\mathrm{m}$ . All GFETs had the same contact width ( $\sim$ 50  $\mu\mathrm{m}$ ) regardless of the stripe width. The channel width  $W=2W_s$ . (c) Scanning electron microscopy image of the central part of one the fabricated GFETs with the gate length  $L=1~\mu\mathrm{m}$ . The underlap is  $u=100~\mathrm{nm}$ .

ranges from <1<sup>13, 14</sup> to  $\sim$ 1.5<sup>15, 16</sup> to 3.3<sup>17</sup>. However, the highest measured extrinsic  $f_{\text{max}}$  was 21.3 GHz highlighting the need for alternative substrates with less charge traps  $f_{\text{max}}$  and cleaner graphene transfer process  $f_{\text{max}}$  and  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  and cleaner graphene transfer process  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates with less charge traps  $f_{\text{max}}$  is the need for alternative substrates  $f_{\text{max}}$  is the need for all  $f_{\text{max}}$  is the need for alternative substrates  $f_{\text{max}}$  is the need for alternative  $f_{\text{max}}$  is the need for alternative substrates  $f_{\text{max}}$  is the need for alternative  $f_{\text{max}}$  is the need for alternative  $f_{\text{max}}$  is the need for alternative  $f_{\text{$

GFETs comprising the same type of gate insulator have been successfully implemented in the past in more complex circuits like integrated inverters and ring oscillators capable of performing signal generation up to  $4.3\,\mathrm{GHz^{18}}$ , voltage gain up to  $13\,\mathrm{or}\,22.3\,\mathrm{dB^{19}}$ , mixing and modulation. However, a direct investigation of the high frequency performance of these GFETs has not been performed so far. In this work, different figures of merit, such as  $f_{\mathrm{max}}$ ,  $f_{\mathrm{D}}$ ,  $A_{\mathrm{V}}$  and  $S_{\mathrm{21}}$ , were extracted from the S-parameter measurements of the individual GFETs to investigate their performance and scaling.

# Experimental

Monolayer graphene grown by chemical vapor deposition (CVD) on Cu was used in the fabrication of the investigated coplanar GFETs. After the growth, graphene was transferred to high-resistivity ( $\sim$ 5 k $\Omega$ cm) Si substrates with a 1  $\mu$ m thick top layer of SiO<sub>2</sub> by a wet process<sup>4</sup>. The graphene stripes were defined by e-beam lithography followed by reactive ion etching in oxygen plasma. The coplanar GFETs were fabricated as depicted in Fig. 1. The channel width W was 10, 40 and 100  $\mu$ m while the gate length L was 0.8, 0.9, 1, 1.1 and 2.2  $\mu$ m. Top gates were patterned by e-beam lithography followed by e-beam evaporation of 100 nm of Al. A thin ( $t_{ox} \sim 4$  nm) native layer of AlO<sub>x</sub> was formed on all surfaces of the Al gates (including the surface at the interface with graphene) by exposing the samples to air<sup>8, 20-23</sup>. The source/drain contacts were fabricated in the final e-beam lithography step, separated by a very small underlap ( $u \sim 100 \,\mathrm{nm}$ ) from the gate. Such underlaps introduce access resistances between the source/drain and gate which cannot be gated and therefore reduce transconductance and gain. The access resistances can be eliminated by a self-aligned transistor layout<sup>4, 21</sup> in which the source and drain are overlapped with the gate. However, we found that overlaps introduce additional parasitic capacitances which have more detrimental effect on the high-frequency response of the transistors than access resistances. Typically, self-aligned GFETs with overlapped gate and source/drain exhibited  $\sim$ 3 times smaller  $f_{max}$  compared to GFETs with (small) underlaps. Such deterioration of the high-frequency response has not been observed in self-aligned T-gate GFETs on flexible substrates<sup>23</sup>. This is probably because the sufficiently large underlaps have been created by shadowing the evaporated source/drain material by the T-gates<sup>23</sup>. The source/drain contacts were made of Au (100 nm thick, without an additional adhesion layer) because we found that pure Au<sup>7</sup> provides the lowest contact resistance to graphene (~250  $\Omega\mu$ m) among the several tested metal combinations (e.g., Ti/Au, Ni/Au, Pd/Au).

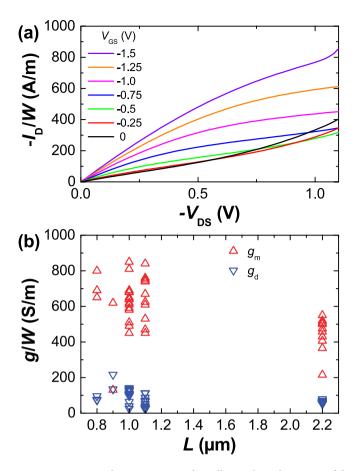

Figure 2. Output characteristics and small-signal conductances of the fabricated GFETs in ambient air. (a) Drain current  $I_{\rm D}$  as a function of  $V_{\rm DS}$  for different  $V_{\rm GS}$  in a GFET with  $W=10\,\mu{\rm m}$  and  $L=1\,\mu{\rm m}$ . The onset of saturation is at  $V_{\rm DS}=V_{\rm GS}-V_0$  and it moves to larger  $|V_{\rm DS}|$  at larger  $|V_{\rm GS}|$ . (b) The transconductance  $g_{\rm m}$  and output conductance  $g_{\rm d}$  of the fabricated GFETs at the operating point at which they exhibit the largest voltage gain  $A_{\rm v}$ .

### **Results and Discussion**

All GFETs were initially characterized at dc to find the optimum biasing conditions for the S-parameter characterization. In ambient air, most of the fabricated GFETs exhibited p-type behavior at low biases with the Dirac voltage  $V_0 \sim 0.25$  V. A small hysteresis was observed in the dc characteristics of the GFETs. The shift of the Dirac voltage was ~12% of the  $V_{\rm GS}$  sweeping range and it did not have any influence on  $g_{\rm m}$  and  $g_{\rm d}$ . We found that the transconductance of the GFETs was larger in the p-type regime ( $V_{\rm GS} < V_0$ ) than in the n-type regime ( $V_{\rm GS} > V_0$ ). This can be attributed to the larger contact resistance in the n-type regime due to the formation of a "pnp" junction between the large workfunction Au contacts and the n-type channel<sup>24,25</sup>. Moreover, the hole mobility was also found to be slightly larger than the electron mobility, as expected for graphene deposited on SiO<sub>2</sub> substrates<sup>26,27</sup>. Therefore, the GFETs were biased in the p-type regime to maximize the transconductance during the S-parameter characterization. In order to also minimize the output conductance, the GFETs were measured in the p-type saturation regime ( $V_{\rm DS} < V_{\rm GS} - V_0 < 0$ ). S-parameter measurements were performed in a Cascade Microtech Summit 12561B probe station. Input and output ac signals were applied by Anritsu Vectorstar MS4647A vector network analyzer. Gate and drain dc biasing was applied by Keithley 2600 source meters. The GFETs were probed by Cascade Microtech 110-A probes with a 100  $\mu$ m-pitch.

Figure 2 shows the output characteristics and conductance of a typical GFET with  $L=1~\mu m$  and  $W=10~\mu m$  for several negative values of  $V_{\rm GS}$ , i.e., for transistor operation deep into the p-type regime. Additional advantage of operating p-doped GFETs in the p-type regime is that larger drain currents  $I_D$  can be reached compared to the n-type regime. This is because larger values of  $|V_{\rm GS}-V_0|$  for  $V_0>0$  can be obtained for negative  $V_{\rm GS}$  than for positive  $V_{\rm GS}$  since  $|V_{\rm GS}|$  is limited by the breakdown voltage  $V_{\rm b}$  of the gate oxide (here  $V_{\rm b}=2.9~\rm V$ ). At small  $|V_{\rm DS}|$ , the graphene channel is uniformly p-doped and the GFET is in the ohmic regime exhibited by the linear  $I_{\rm D}-V_{\rm GS}$  curves. A larger  $|V_{\rm DS}|$  reduces the hole concentration near the drain leading to charge neutrality and the onset of saturation at  $V_{\rm DS}=V_{\rm GS}-V_0$ . At even larger  $|V_{\rm DS}|$ , the charge neutrality point moves towards source with electron accumulation on the drain side. However, as long as  $|V_{\rm DS}|$  is not too large, the electron accumulation is not significant and the output conductance approaches zero reflecting strong current saturation. In this regime, the thin dielectric exerts strong capacitive control over the drain current leading to a larger channel depletion rate which improves the drain current saturation is lost due to significant

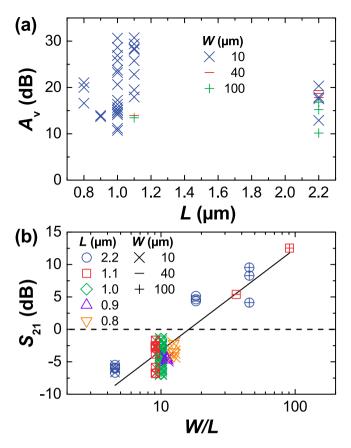

**Figure 3.** The highest gain in each of the fabricated GFETs at 10 MHz. (a) The open circuit voltage gain  $A_{\rm v}$  as a function of the gate length L. (b) The forward gain  $S_{21}$  as a function of W/L. The highest value of 12.5 dB was obtained for  $W=100\,\mu{\rm m}$  and  $L=1.1\,\mu{\rm m}$ . A W/L fit is suggested by the black line because  $S_{21}$  scales with  $g_{\rm m}$  and therefore with W/L.

electron accumulation between the charge neutrality point and drain. This can be observed in the first three plotted curves ( $|V_{CS}| \le 0.5 \,\mathrm{V}$ ) in Fig. 2(a).

The highest values of the open-circuit voltage gain  $A_{\rm v}=|Z_{21}|/|Z_{11}|$  measured for each of the fabricated GFETs are shown in Fig. 3(a). The gain was extracted from the S-parameter measurements of the GFETs biased at negative  $V_{\rm DS}$  and  $V_{\rm GS}$ . The open-circuit voltage gain is equal to the intrinsic transistor gain  $A=g_{\rm m}/g_{\rm d}$  at low frequencies. The intrinsic gain A is not expected to scale with W or L because  $g_{\rm m}$  scales with W/L while  $g_{\rm d}$  approximately scales with W/L. However, due to the influence of the contact resistance, the intrinsic gain A and consequently  $A_{\rm v}$  were smaller at shorter L. The largest measured  $A_{\rm v}$  was above 30 dB at 10 MHz for GFETs with  $L\sim 1\,\mu{\rm m}$  and  $W=10\,\mu{\rm m}$ . This is the highest voltage gain reported for GFETs so far<sup>9-11</sup>. The notable scatter of gain values can be attributed to device-to-device variability from the intrinsic non-uniformity of CVD graphene and contact misalignment. Due to the inherent overlay error of the e-beam exposure system, the perfect alignment between the gate and source/drain contacts, as shown in Fig. 1(c), was not possible in all fabricated GFETs. This led to the scatter in the measured data because, e.g., smaller underlap (or even unintentional overlap) reduced access resistances and therefore increased  $A_{\rm v}$  and  $S_{21}$ , but at the same time reduced  $f_{\rm T}$  and  $f_{\rm max}$  due to the increase of parasitic capacitances.

The measured forward transmission coefficient  $S_{21}$  as a function of W/L is shown in Fig. 3(b). This coefficient reflects the real power amplification as  $|S_{21}|^2$  is equal to the transducer power gain of a two-port network. We found that  $|S_{21}|$  scales with W/L which was expected as it is proportional to  $g_{\rm m}$ . The narrowest devices ( $W=10~\mu{\rm m}$ ) exhibited  $|S_{21}|<0$  dB, i.e., power attenuation. The highest measured value was 12.5 dB at 10 MHz for 10 times wider devices. This is also the highest  $|S_{21}|$  reported in literature for a graphene channel with  $W=100~\mu{\rm m}^{12}$ .

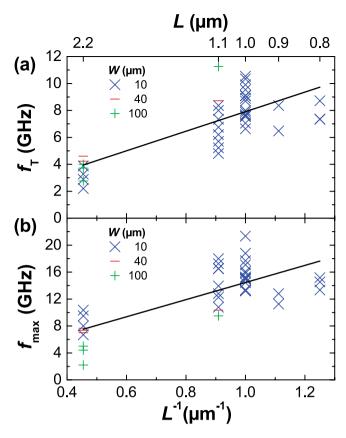

Figure 4(a) shows the cutoff frequency  $f_{\rm T}$  measured on each GFET and plotted as a function of the gate length L. The highest measured  $f_{\rm T}$  was 10.3 GHz in a device with  $W=10~\mu{\rm m}$  and  $L=1~\mu{\rm m}$ . The cutoff frequency is strongly affected by relatively low charge-carrier mobility ( $\mu$ < 1000 cm²/(Vs)). Mobilities above 5000 cm²/(Vs) have been obtained in CVD graphene deposited on SiO<sub>2</sub><sup>26, 27</sup>, but the top gate introduces charge traps at the interface with graphene that act as scattering centers degrading transistor performances. The cutoff frequency  $f_{\rm T}$  was found to scale approximately with  $L^{-1}$ , as suggested by the black line in Fig. 4(a). However, the scaling trend is not preserved at submicron gate lengths due to the increased influence of contact resistance in shorter devices.

**Figure 4.** The largest values of the high-frequency transistor response parameters of each fabricated GFET as a function of gate length L. (a) The cuttof frequency  $f_{\rm T}$  and (b) maximum oscillation frequency  $f_{\rm max}$ . A  $L^{-1}$  fit is suggested by the black line in both plots.

Figure 4(b) shows the highest measured maximum oscillation frequency  $f_{\rm max}$  obtained for each GFET and plotted as a function of the gate length L. The highest measured extrinsic  $f_{\rm max}$  was 21.3 GHz in a GFET with  $W=10~\mu{\rm m}$  and  $L=1~\mu{\rm m}$  (discussion on the intrinsic  $f_{\rm max}$  can be found in the Supplementary information). The obtained values are comparable to those of GFETs with the same gate length  $^{14,16,28}$ . Even though it has previously been found that  $f_{\rm max}$  does not scale very well with the gate length in GFETs<sup>28</sup>, we observed a gate-length dependence  $L^{-1}$  down to  $0.8~\mu{\rm m}$ , despite noticeable degradation in submicron devices. We obtained larger  $f_{\rm max}$  in narrower devices confirming expected scaling  $f_{\rm max} \propto R_{\rm g}^{-1/2} \propto W^{-1/2}$ , where  $R_{\rm g}$  is the gate resistance<sup>28</sup>. Even larger  $f_{\rm max}$  can be obtained if the contact and gate width are adjusted to the actual channel width (i.e., not as in the presented GFETs in which the same metal layout shown in Fig. 1 was used regardless of the channel width). In such devices, the highest measured  $f_{\rm max}$  was 26 GHz with  $W=10~\mu{\rm m}$  and  $L=1~\mu{\rm m}$ . However, in general, narrower channels result in smaller gain  $|S_{21}|$ , i.e., there is a tradeoff between  $|S_{21}|$  and  $f_{\rm max}$ .

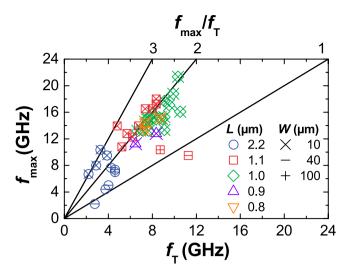

channels result in smaller gain  $|S_{21}|$ , i.e., there is a tradeoff between  $|S_{21}|$  and  $f_{\rm max}$ . Figure 5 shows the maximum oscillation frequency  $f_{\rm max}$  as a function of the cutoff frequency  $f_{\rm T}$ . Larger ratio  $f_{\rm max}/f_{\rm T}$  usually indicates better drain current saturation because, to a first approximation,  $f_{\rm max}/f_{\rm T} \propto g_{\rm d}^{-1/2.28}$ . In InP and GaAs high electron mobility transistors, the fastest available technologies,  $f_{\rm max}/f_{\rm T} \sim 2^{28}$ , with the highest measured value of 3.1 in InP transistors exhibiting  $f_{\rm max}=1.2\,{\rm THz^{29}}$ . In most of the GFETs realized so far,  $f_{\rm max}$  is usually smaller than  $f_{\rm T}^{13,14}$ . A ratio of 1.5 has been obtained in GFETs by reducing the gate resistance through a T-gate structure  $f_{\rm T}^{15,16}$ . The highest ratio reported so far in GFETs has been 3.3 but it has been obtained at  $f_{\rm T}^{15,16}$ . The highest ratio reported so far in GFETs has been 3.2, with an average value of 2 for GFETs with  $f_{\rm T}^{15,16}$ . The highest ratio reported to the state of the art GFETs because all our measurements were performed at  $f_{\rm T}^{15,16}$  and therefore, an improvement of cutoff frequency by mobility enhancement and contact resistance reduction are expected to increase  $f_{\rm T}^{15,16}$  and therefore to increase  $f_{\rm T}^{15,16}$  beyond that of the state of the art GFETs.

# Conclusion

We have demonstrated GFETs with a thin layer of  $AlO_x$  ( $t_{\rm ox}=4\,{\rm nm}$ ) gate dielectric. The fabricated GFETs exhibit intrinsic gain  $g_{\rm m}/g_{\rm d}>30$  dB, forward gain  $S_{21}\sim12\,{\rm dB}$ , and ratio  $f_{\rm max}/f_{\rm T}\sim3$ , at different transistor geometries. The highest  $f_{\rm max}=21.3\,{\rm GHz}$  was obtained at a gate length  $L=1\,\mu{\rm m}$  indicating adverse influence of contact resistance at shorter gate lengths. However, the critical technological parameters that should be optimized to improve  $f_{\rm max}$  have been identified and they are mostly technological rather than fundamental in nature. The

**Figure 5.** The maximum oscillation frequency  $f_{\max}$  as a function of the cutoff frequency  $f_{\text{T}}$  of each fabricated GFET for different gate lengths L and channel widths W. The ratio  $f_{\max}/f_{\text{T}}$  varies between 1 and 3.

quality of CVD graphene should be enhanced to provide better homogeneity, allowing a more accurate study of the improvement of transistor performance with scaling. Smoother substrates and less defective interfaces should be used to reduce the scattering and increase carrier mobility. Contact resistance should be reduced below  $100\,\Omega\mu\mathrm{m}$  to simultaneously improve gain and frequency performances. Finally, the gate resistance should be reduced to enhance  $f_{\mathrm{max}}$ , which can be accomplished through a T-gate structure. Our study has therefore also served to emphasize several remaining challenges of graphene technology which should be overcome to further expand applications of GFETs in electronics.

## References

- 1. Mayorov, A. S. et al. Micrometer-scale ballistic transport in encapsulated graphene at room temperature. Nano Lett. 11, 2396–2399, doi:10.1021/nl200758b (2011).

- 2. Novoselov, K. S. et al. Two-dimensional gas of massless dirac fermions in graphene. Nature 438, 197–200, doi:10.1038/nature04233 (2005).

- 3. Dorgan, V. E., Bae, M.-H. & Pop, E. Mobility and saturation velocity in graphene on SiO<sub>2</sub>. Appl. Phys. Lett. **97**, 082112, doi:10.1063/1.3483130 (2010).

- 4. Rizzi, L. G. et al. Cascading wafer-scale integrated graphene complementary inverters under ambient conditions. Nano Lett. 12, 3948–3953, doi:10.1021/nl301079r (2012).

- 5. Dean, C. R. et al. Boron nitride substrates for high-quality graphene electronics. *Nature Nanotech* 5, 722–726, doi:10.1038/nnano.2010.172 (2010).

- 6. Han, S.-J., Reddy, D., Carpenter, G. D., Franklin, A. D. & Jenkins, K. A. Current saturation in submicrometer graphene transistors with thin gate dielectric: Experiment, simulation, and theory. ACS Nano 6, 5220–5226, doi:10.1021/nn300978c (2012).

- 7. Guerriero, E. et al. Gigahertz integrated graphene ring oscillators. ACS Nano 7, 5588-5594, doi:10.1021/nn401933v (2013).

- English, C. D., Smithe, K. K., Xu, R. & Pop, E. Approaching ballistic transport in monolayer MoS<sub>2</sub> transistors with self-aligned 10 nm top gates. In Int. El. Devices Meet., 5.6.1–5.6.4 (San Francisco, CA, USA, 2016).

- 9. Wu, Y. et al. State-of-the-art graphene high-frequency electronics. Nano Lett. 12, 3062–3067, doi:10.1021/nl300904k (2012).

- 10. Tao, L. et al. Inductively heated synthesized graphene with record transistor mobility on oxidized silicon substrates at room temperature. Appl. Phys. Lett. 103, doi:10.1063/1.4828501 (2013).

- 11. Song, S. M., Bong, J. H., Hwang, W. S. & Cho, B. J. Improved drain current saturation and voltage gain in graphene-on-silicon field effect transistors. *Sci. Rep.* 6, 25392, doi:10.1038/srep25392 (2016).

- 12. Habibpour, O. Graphene FETs in Microwave Applications. Ph.D. thesis, Chalmers University of Technology (2012).

- 13. Lin, Y.-M. et al. 100-GHz transistors from wafer-scale epitaxial graphene. Science 327, 662–662, doi:10.1126/science.1184289 (2010).

- Guo, Z. et al. Record maximum oscillation frequency in C-face epitaxial graphene transistors. Nano Lett. 13, 942–947, doi:10.1021/nl303587r (2013).

- 15. Han, S. J., Oida, S., Jenkins, K. A., Lu, D. & Zhu, Y. Multifinger embedded T-shaped gate graphene RF transistors with high  $f_{\text{MAX}}/f_{\text{T}}$  ratio. *IEEE Electron Device Lett.* **34**, 1340–1342, doi:10.1109/LED.2013.2276038 (2013).

- Wu, Y. et al. 200 GHz maximum oscillation frequency in CVD graphene radio frequency transistors. ACS Appl. Mater. Interfaces 8, 25645–25649, doi:10.1021/acsami.6b05791 (2016).

- 17. Moon, J. et al. Epitaxial-graphene RF field-effect transistors on Si-face 6H-SiC substrates. IEEE Electron Device Lett. 30, 650–652, doi:10.1109/LED.2009.2020699 (2009).

- 18. Bianchi, M. et al. Scaling of graphene integrated circuits. Nanoscale 7, 8076-8083, doi:10.1039/C5NR01126D (2015).

- 19. Fiocco, M., Guerriero, E., Sagade, A. A., Neumaier, D. & Sordan, R. Integrated graphene high-gain voltage amplifiers and ring oscillators. In 4th Graphene International Conference, Toulouse, France, May 2014 (2014).

- Miyazaki, H., Li, S., Kanda, A. & Tsukagoshi, K. Resistance modulation of multilayer graphene controlled by the gate electric field. Semicond. Sci. Technol. 25, 034008, doi:10.1088/0268-1242/25/3/034008 (2010).

- $21. \ Guerriero, E.\ et\ al.\ Graphene\ audio\ voltage\ amplifier.\ Small\ 8,357-361, \\ doi: 10.1002/smll.201102141\ (2012).$

- 22. Lu, C.-C., Lin, Y.-C., Yeh, C.-H., Huang, J.-C. & Chiu, P.-W. High mobility flexible graphene field-effect transistors with self-healing gate dielectrics. ACS Nano 6, 4469–4474, doi:10.1021/nn301199j (2012).

- 23. Yeh, C.-H. et al. Gigahertz flexible graphene transistors for microwave integrated circuits. ACS Nano 8, 7663–7670, doi:10.1021/nn5036087 (2014).

- Knoch, J., Chen, Z. & Appenzeller, J. Properties of metal-graphene contacts. IEEE Trans. Nanotechnol. 11, 513–519, doi:10.1109/ TNANO.2011.2178611 (2012).

- 25. Liu, W., Wei, J., Sun, X. & Yu, H. A study on graphene-metal contact. Crystals 3, 257-8, doi:10.3390/cryst3010257 (2013).

- Novikov, D. S. Numbers of donors and acceptors from transport measurements in graphene. Appl. Phys. Lett. 91, 102102, doi:10.1063/1.2779107 (2007).

- 27. Chen, J.-H. et al. Charged-impurity scattering in graphene. Nature Phys. 4, 377-381, doi:10.1038/nphys935 (2008).

- 28. Schwierz, F. Graphene transistors: Status, prospects, and problems. *Proc. IEEE* 101, 1567–1584, doi:10.1109/JPROC.2013.2257633 (2013).

- Lai, R. et al. Sub 50 nm InP HEMT device with Fmax greater than 1 THz. In Int. El. Devices Meet. 609-611, doi:10.1109/ IEDM.2007.4419013 (2007).

# **Acknowledgements**

The authors would like to thank D. Neumaier for substrates. This work was supported in part by EU Graphene Flagship (grant No. 696656) and US Air Force (grant No. FA9550-14-1-0251).

### **Author Contributions**

R.S. and H.Z. conceived the experiments, A.B., E.A.C., A.P., A.C. and A.Z. grew and transferred graphene, E.G., P.P. and A.M. fabricated GFETs, E.G., A.M. and O.H. conducted the measurements, and E.G., A.M., O.H., M.W., N.R., E.P., H.Z. and R.S. analysed the results. R.S. and E.G. wrote the manuscript and all authors reviewed the manuscript.

### Additional Information

**Supplementary information** accompanies this paper at doi:10.1038/s41598-017-02541-2

**Competing Interests:** The authors declare that they have no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2017